AVR ATtiny2313

データシートなどからその概要

| メモリ | 2kバイトフラッシュメモリ 128バイトEEPROM 128バイトSRAM |

|

| タイマ | 同様機能のタイマー0(8ビット)と タイマー1(16ビット) が1つずつ 4つのPWM出力可能 タイマー1にはインプットキャプチャがある |

|

| IO | 18本 | |

| アナログコンパレータ | あり | |

| A/D変換 | ナシ | |

| ウオッチドッグ | 専用発信器つきWDTあり | |

| 通信 | USI と USRT(全二重) |

|

| RC発信器内蔵 | 校正付き 8M、4MHz | |

| 動作電圧 | 1.8-5.5V(2313V) 2.7-5.5V(2313) |

●ヒューズビット

上位バイト

下位バイト

内部発振器の校正

工場出荷時の内部発振の誤差を調整するためのレジスタ

| 名称 | ビット | 意味 | 規定値(出荷時) |

| DWNEN | 7 | デバッグWIRE機能許可(0:有効、1:無効) | 1(デバッグWIRE不可) |

| EESAVE | 6 | チップ消去からEEPROM内容保護(0:保護、1:未保護) | 1(未保護) |

| SPIEN | 5 | シリアルプログラミング許可(0:ISP許可、1:ISP禁止) | 0(許可) |

| WDTON | 4 | ウオッチドッグ有効(0使用する、1:使用しない) | 1(WDTはWDTCSR レジスタで設定) |

| BODLEVEL3 | 3 | 3 2 1 1 1 1 :リセット禁止 1 1 0 :1.8Vリセット 1 0 1 :2.7Vリセット 1 0 0 :4.3Vリセット |

1(未設定) |

| BODLEVEL2 | 2 | 1(未設定) | |

| BODLEVEL1 | 1 | 1(未設定) | |

| RSTDISBL | 0 | PA2がIOピンか(0)、RESET設定か(1) | 1(RESET設定) |

下位バイト

| 名称 | ビット | 意味 | 規定値 |

| CKDIV8 | 7 | システムクロック8分周選択(0 : 1/8、 1: 1) | 0 |

| CKOUT | 6 | システムクロック出力許可(0:出力する、1:しない) | 1 |

| SUT1 | 5 | 1 0 (詳細は日データシートP15,16) 0 0 : BODリセット許可 0 1 : 高速立ち上がり電源 1 0 : 低速立ち上がり電源 1 1 : --- |

1(低速立ち上がり) |

| SUT0 | 4 | 0 | |

| CKSEL3 | 3 | 3 2 1 0 1 × × × : 外部発振 0 1 1 0 : 128k内部WDT発振 0 1 0 0 : 8M内部発振 0 0 1 0 : 4M内部発振 0 0 0 0 : 外部クロック信号 (詳細は日データシートP14,15,16) |

0(8M内部発振) |

| CKSEL2 | 2 | 1 | |

| CKSEL1 | 1 | 0 | |

| CKSEL0 | 0 | 0 |

内部発振器の校正

工場出荷時の内部発振の誤差を調整するためのレジスタ

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| - | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 | |

| 初期値(デフォルト) 0 このビットに1つでも1を書くと周波数が増加する 調整値 下表 |

||||||||

| OSCCAL値 | 公称周波数に対する割合 | |

| MIN | MAX | |

| $00(b:00000000) | 50% | 100% |

| | | | | | |

| $3F(b:00111111) | 75% | 150% |

| $7F(b:1111111) | 100% | 200% |

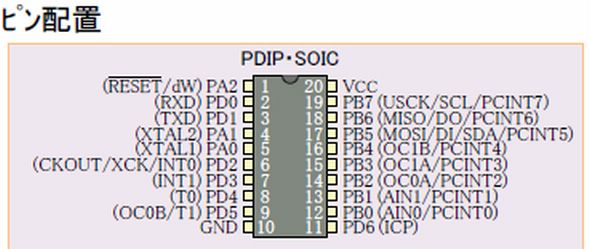

●IOピン

PA(ポートA)、PB(ポートB)、PD(ポートD) と18本まで可能。

すべてのポートに内部プルアップ設定が可能

IOポート設定は少しPICなどと違うところがあり

データレジスタが出力用と読み取り(入力)用に分かれていて、別レジスタでする

- ポートB出力レジスタ PORTB (ポートAならPORTA)

- ポートB読み取り(入力)レジスタ PINB (ポートAならPINA)

そして変則的 ポート設定方法になっているところもある

- 方向設定レジスタ(DRR×) を入力設定にして

データレジスタ(PORT×)で1にすると 内部プルアップ設定になる。 - 方向設定レジスタ(DRR×)を出力設定にして

入力用データレジスタ(PIN×)で1にすると 出力データが反転になる。

ISP書き込みピンは

SCL、MOSI、MISO、RST(RESET)

●メモリ配置

フラッシュメモリ

1万回の書き換え可能

1k×16ビットで構成

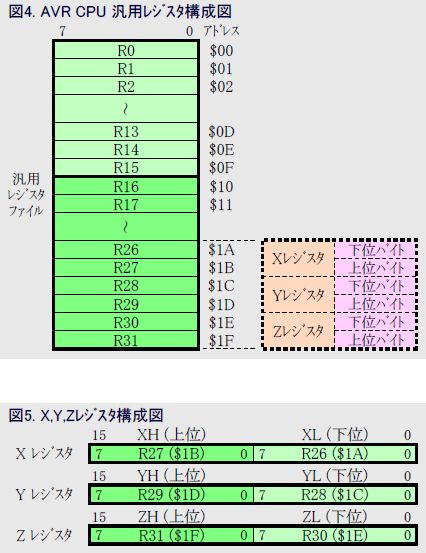

32バイトの汎用レジスタ

でも全部同様に使えるわけでなく、制限がいろいろあります

汎用レジスタの項目参照

SRAMが$0060から。

直接アドレッシングでどこでも指定可能

(全体を網羅)

汎用レジスタ 32コ

でもいろんな制限あり (*更に下 参照 )

下のX,Y,Zレジスタに分類されるものは

2バイトくっつけて、インデックススレジスタとしても使用

32コもある汎用レジスタですが、いっぱいある! と喜んでもいられない制限があります。

汎用レジスタも区分により、いろんな制限があってなかなか複雑です。

アルゴ算法堂 では使用命令の制限がきれいに表になっていたので、そのまま使わせてもらいました。

これはまた なかなかハマり込みそうな制限たちです・・

| reg | 命令の制限 | 乗算関係の制限 | ワード演算 | 機能 |

| 0 | LDI、ANDI、CPI、ORI SBCI、SUBI、CBR、 SBR、SER 不可 |

MULS、MULSU、 FMUL、FMULS、 FMULSU 不可 |

ADIW、SBIW 不可 |

乗算結果を格納 プログラムアクセス |

| 1 | ||||

| 2 | ||||

| 3 | ||||

| 4 | ||||

| 5 | ||||

| 6 | ||||

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ||||

| 11 | ||||

| 12 | ||||

| 13 | ||||

| 14 | ||||

| 15 | ||||

| 16 | ||||

| 17 | ||||

| 18 | ||||

| 19 | ||||

| 20 | ||||

| 21 | ||||

| 22 | ||||

| 23 | ||||

| 24 | MULSU、FMUL、 FMULS、FMULSU 不可 |

|||

| 25 | ||||

| 26 | インデックスX | |||

| 27 | ||||

| 28 | インデックスY | |||

| 29 | ||||

| 30 | インデックスZ | |||

| 31 |

参考資料

アルゴ算法堂 H8講座

電子工作-AVR goes on

スポンサーリンク

- twtter

- google+

- hatena